数字密码锁系统的设计代码详见光盘附件5-8。

完成编码设计,运行正确后,在ISE中用HDL描述获得RTL电路,如图5-45所示。数字密码锁共有三个输入端口和两个输出端口,cmd为按键输入端、resetb为清零端、clk是时钟输入信号。两个输出端分别为报警输出alarmed接报警电路、passed为开锁输出接门控电路。

实现数字密码锁功能的FPGA内部结构电路图见光盘附件中附图5-1。

图5-45 RTL电路图

下面分析数字密码锁实现的各种功能。

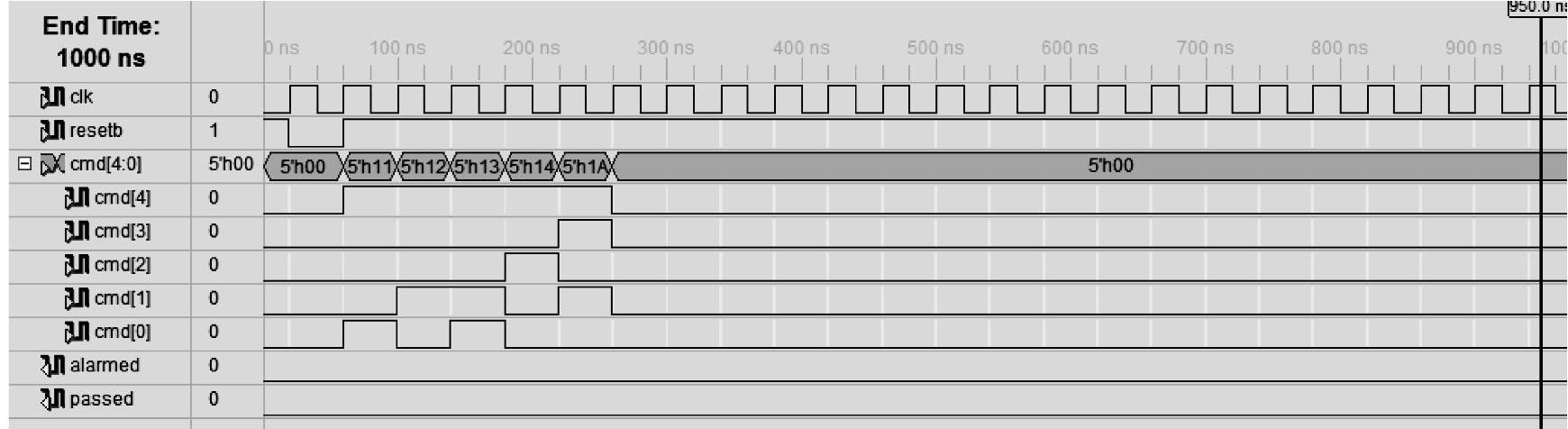

(1)情况一 用户输入正确密码时,设置的激励波形如图5-46所示。

图5-46 激励波形图

仿真结果如图5-47所示。

图5-47 仿真结果

调试结果如图5-48所示。

图5-48 调试结果

由图5-47和图5-48所示的仿真和调试结果可以看出,当输入正确的4位密码时,数字密码锁能正确的进行解锁操作,并发出解锁命令,在解锁一段时间后系统自动恢复至初始状态。

(2)情况二 用户连续输入错误密码三次,设置激励波形如图5-49所示。

图5-49 激励波形图

仿真结果如图5-50、图5-51所示。

(https://www.xing528.com)

(https://www.xing528.com)

图5-50 仿真结果一

图5-51 仿真结果二

调试结果如图5-52所示。

图5-52 调试结果

由图5-50~图5-52可以看出,当用户输入一次错误密码时,系统不会执行解锁命令,同时也没有报警信号的输出,当输入密码错误次数为三次时,系统开始发出报警信号,并且在报警一段时间后会自动解除报警,恢复至初始状态。

(3)情况三 用户输入密码错误时,用cancel来更正,设置的激励波形如图5-53所示。

图5-53 激励波形图

仿真结果如图5-54、图5-55所示。

图5-54 仿真结果一

图5-55 仿真结果二

调试结果如图5-56所示。

图5-56 调试结果

由图5-54~图5-56可以看出,用户在输入第三位密码时,输入错误,用户使用cancel命令删除了第三位输入,重新输入第三位密码,完成密码后,同样可以使程序解锁,并在规定的时间后,重新恢复至初始状态。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。