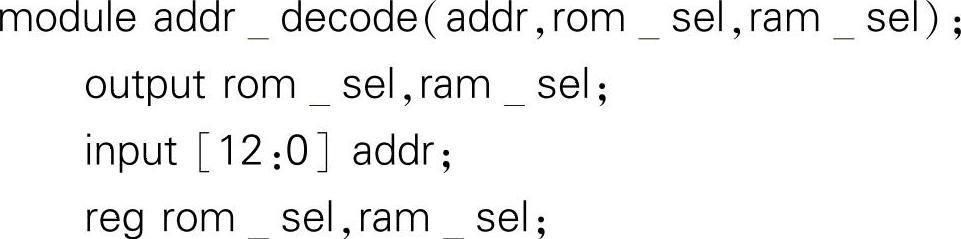

1.地址译码器的实现

外围模块地址译码器的Verilog实现代码如下:

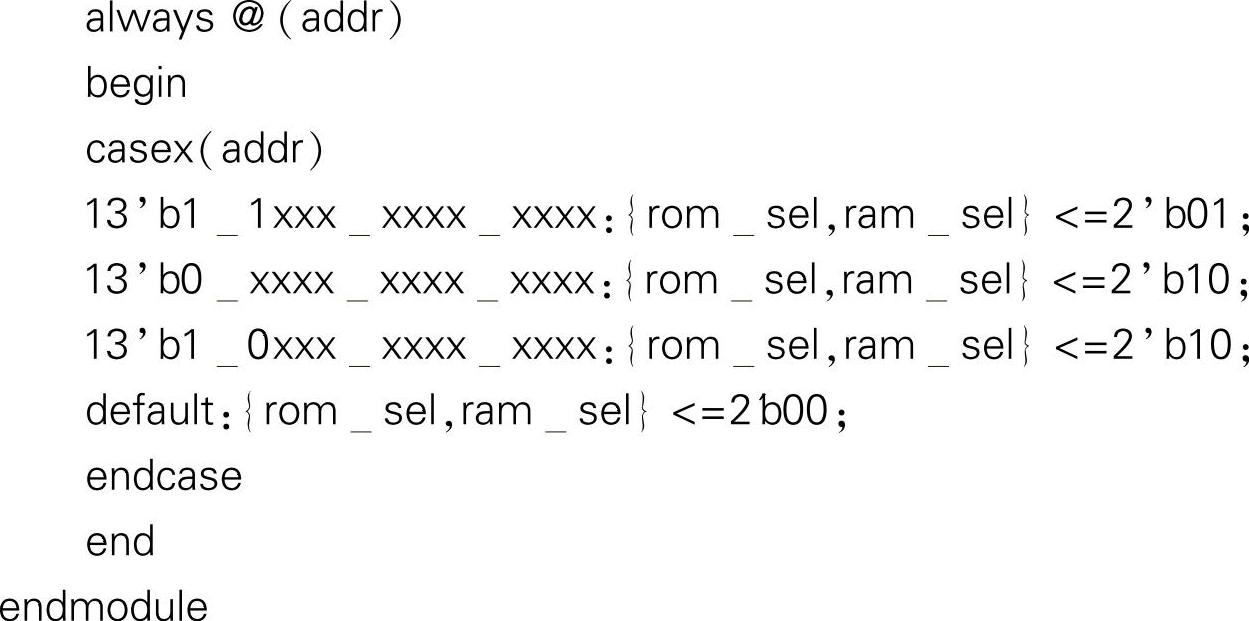

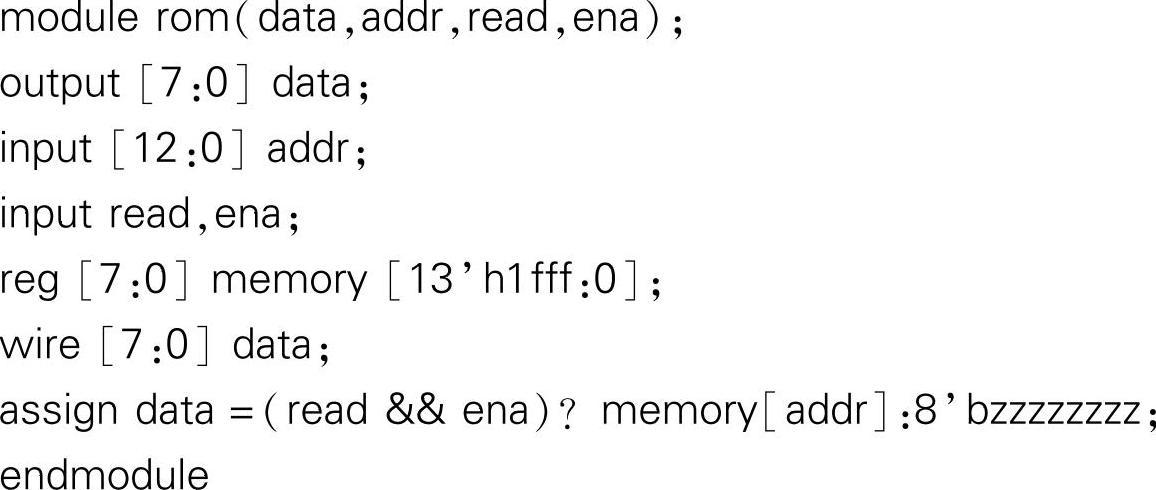

2.RAM的实现

外围模块RAM的Verilog实现代码如下:

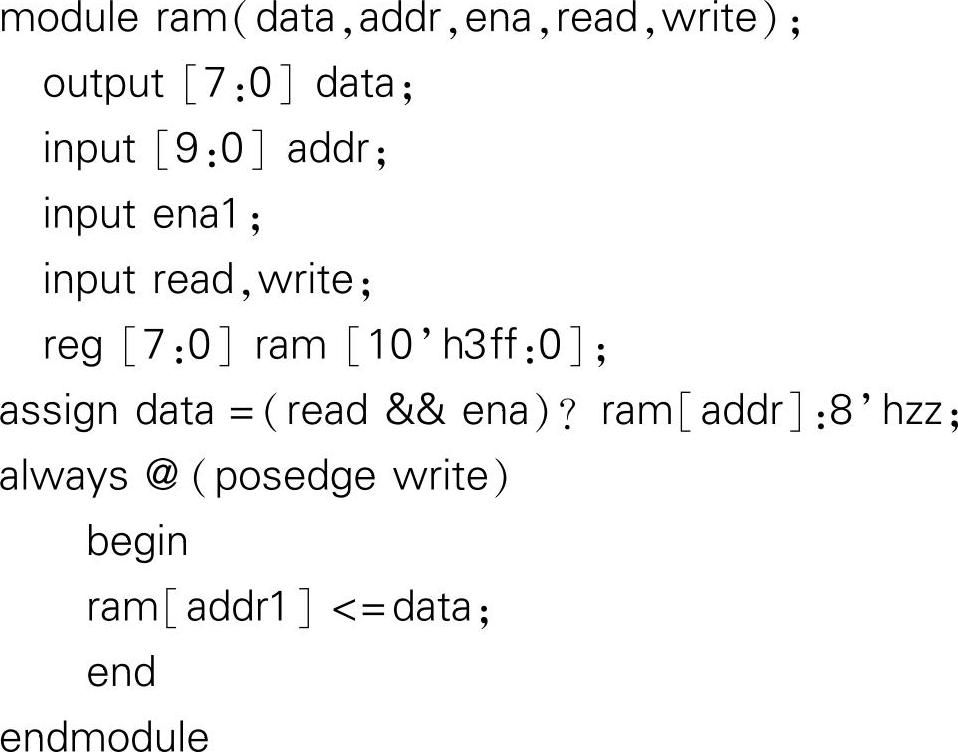

3.ROM的实现

外围模块ROM的Verilog实现代码如下:

4.RISC-CPU的测试

在对RISC-CPU顶层模块进行功能仿真之前,需要先对各个子模块进行仿真,编写每个子模块的测试程序(testbench),然后对其子模块分别进行仿真,确保每个子模块功能正确无误后再对顶层模块进行仿真。子模块的仿真过程比较简单,前面已经介绍过,下面着重介绍RISC-CPU顶层模块的功能仿真。

为了对所设计的RISC-CPU模型进行验证,需要把RISC-CPU包装在一个模块下,这样其内部连线就隐蔽起来了,从系统的角度看显得简洁。还需要建立一些必要的外围器件模型,例如,存储程序用的ROM模型、存储数据用的RAM和地址译码器(地址译码器用于产生选通信号,选通ROM或RAM)等。这些模型都可以用VerilogHDL描述,通过Verilog HDL模块调用的方法把这些外围电路的模块连接上。RISC-CPU测试外围电路连接如图4-51所示。

图4-51 RISC-CPU测试外围电路连接(https://www.xing528.com)

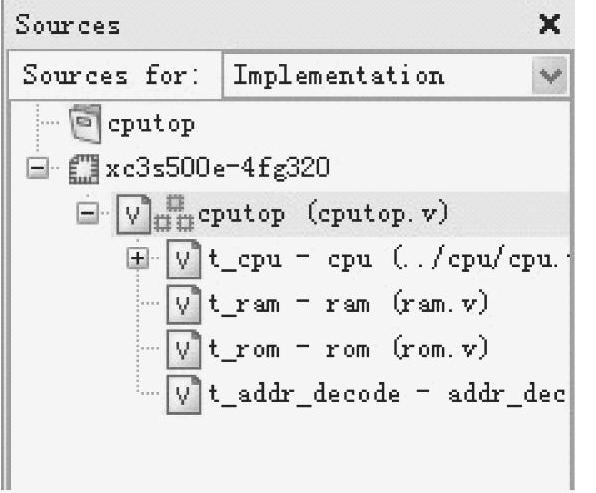

CPUTOP顶层模块由CPU模块、Addr_decode地址译码器模块、RAM模块和ROM模块组成,在ISE11.1仿真软件中,将其各个模块加载到CPUTOP顶层模块中,CPUTOP顶层文件目录如图4-52所示。

CPUTOP顶层模块的测试代码详见光盘附件4-7。

根据CPU的工作周期进行复位与启动、读/写操作三个工作状态的仿真。

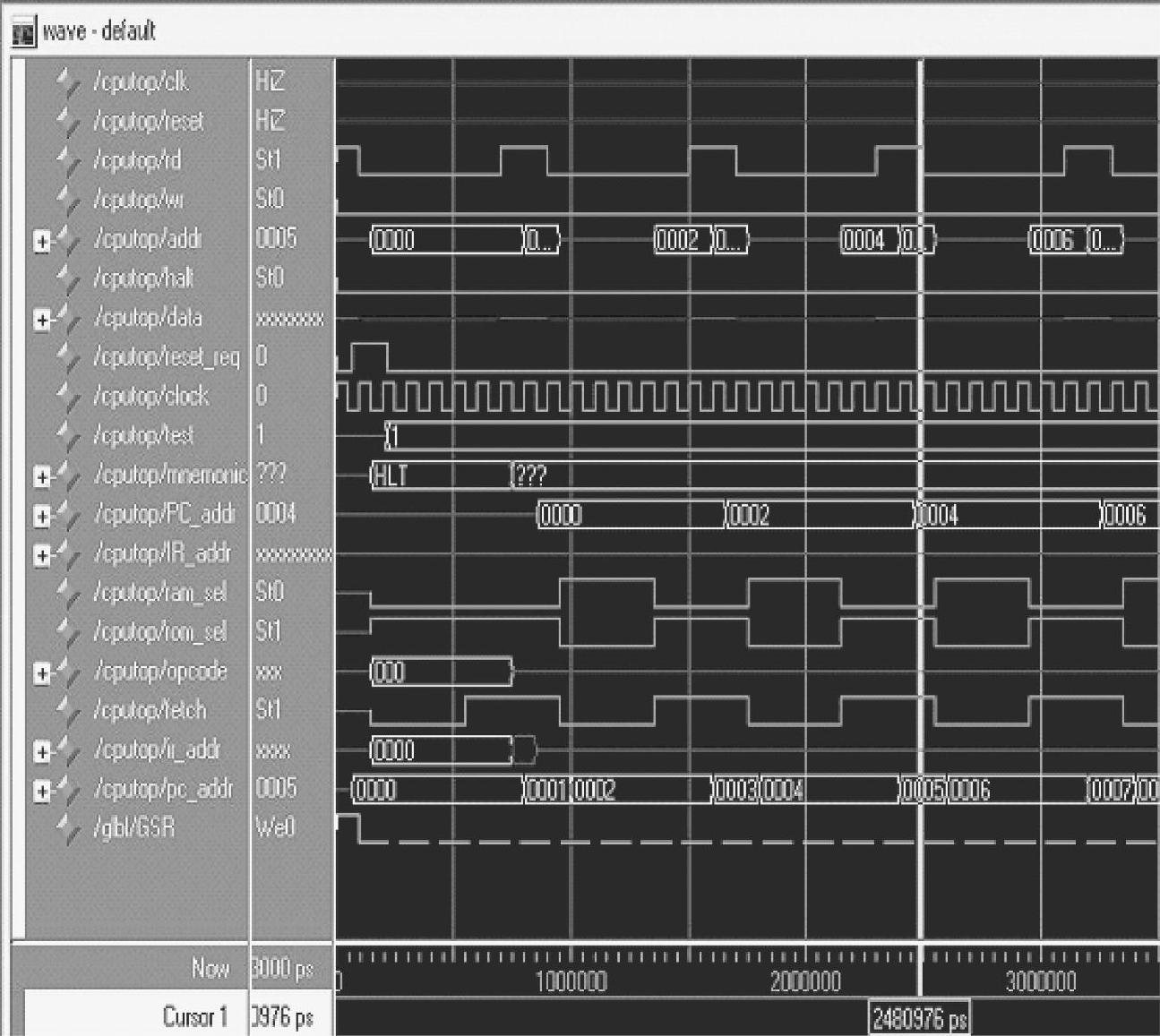

RISC-CPU的复位和启动操作是通过reset引脚的信号触发执行的。当reset信号一进入高电平,RISC-CPU就会结束现行操作,并且只要reset停留在高电平状态,CPU就维持在复位状态。在复位状态,CPU各内部寄存器都设为初值,全部为0。数据总线为高阻态,地址总线为0000H,所有控制信号均为无效状态。reset回到低电平后,接着到来的第一个fetch上升沿将启动RISC-CPU开始工作,从ROM的000处开始读取指令并执行相应操作。CPU复位和启动操作波形如图4-53所示。

图4-52 CPUTOP顶层文件

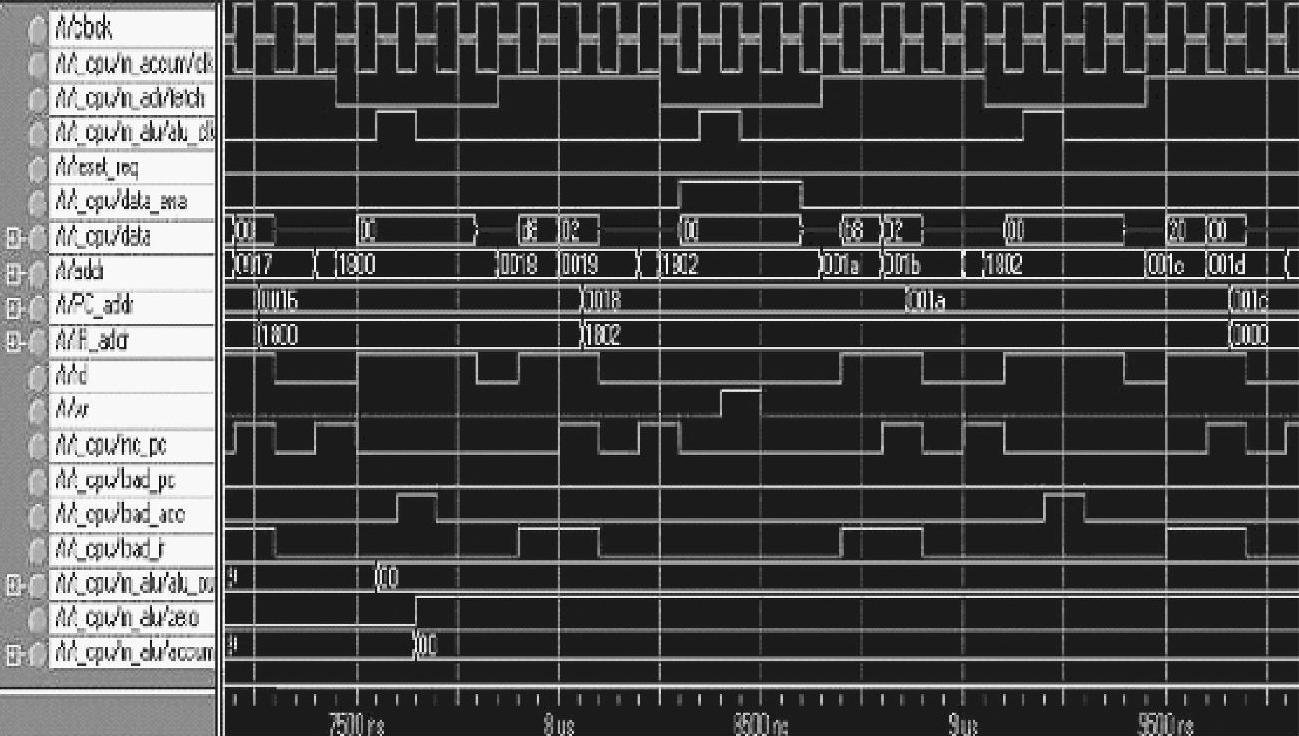

每个指令周期的前第0~3个时钟周期用于读指令,第3.5个周期处,存储器或端口地址就输出到地址总线上。第4~6个时钟周期,读信号rd有效,数据送到数据总线上,以备累加器锁存,或参与算术、逻辑运算。第7个时钟周期,读信号无效,第7.5个周期,地址总线输出PC地址,为下一个指令做好准备。图4-54所示为CPU从存储器或端口读操作波形。

图4-53 CPU复位和启动操作波形

图4-54 CPU读操作波形

每个指令周期的第3.5个时钟周期处,写地址就建立了,第4个时钟周期输出数据,第5个时钟周期输出写信号,至第6个时钟结束,数据无效,第7.5时钟地址输出为PC地址,为下一个指令周期做好准备。图4-55所示为CPU对存储器或端口写操作波形。

图4-55 CPU写操作波形

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。