【摘要】:CPU模块的VerilogHDL实现代码详见光盘附件4-6。CPU模块仿真波形如图4-47所示。由于要对模块进行实时的控制,因此在这里需要一个ICON核、一个ILA核、一个VIO核。将例化模块所用到的代码加到CPU相应的位置,并进行修改,最后得到调用核后的模块形式如图4-48所示。在实现步骤成功后,单击Generate Pro-gramming Files,生成bit流文件。图4-48 CPU的顶层文件及各子模块和调用的核图4-49 VIO核调试结果设置触发条件,然后双击按钮,出现ILA核捕获的数据波形,如图4-50所示。图4-50 ILA核调试结果

CPU模块的VerilogHDL实现代码详见光盘附件4-6。

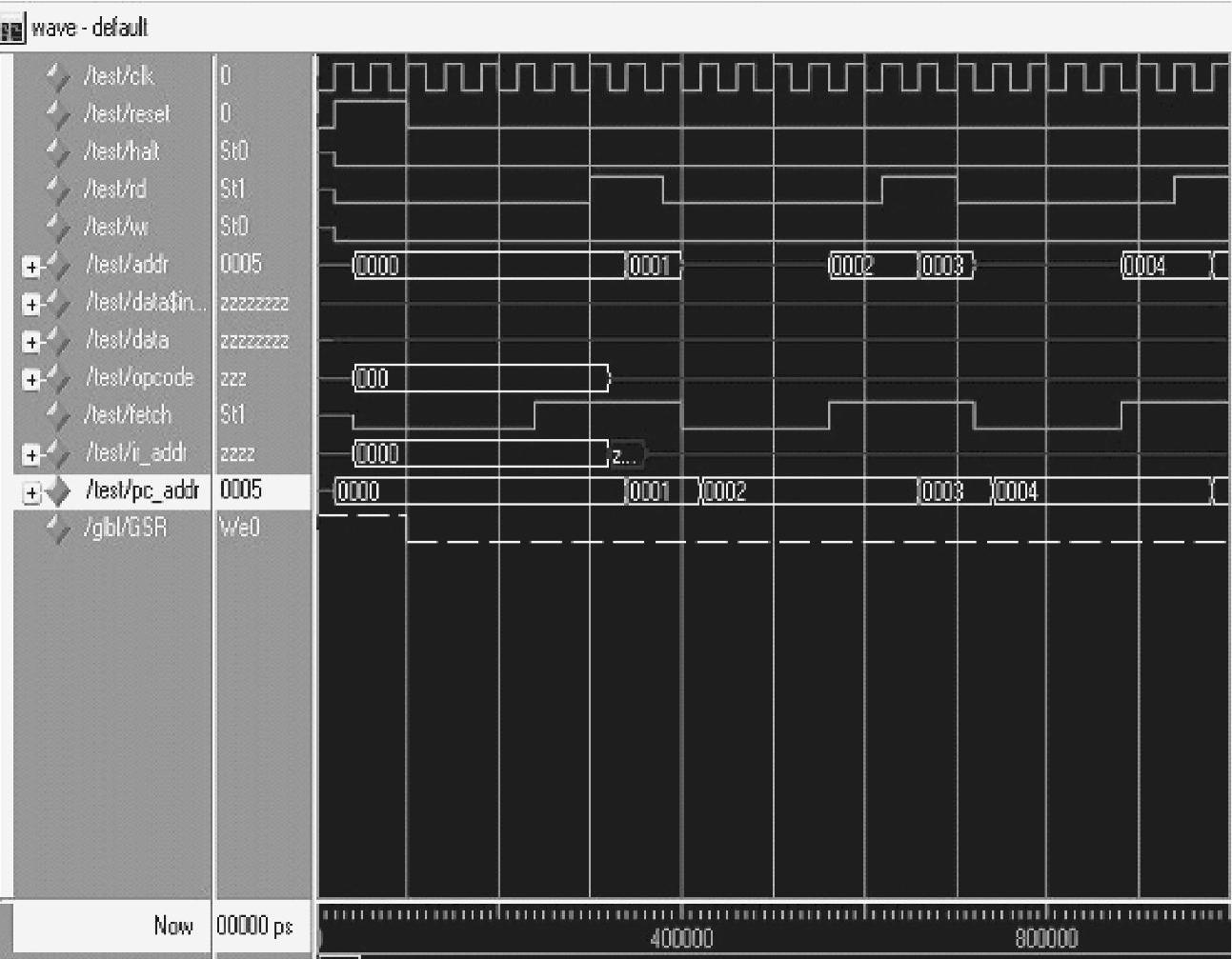

对于整个CPU模块,不仅要观察其输入与输出clk、reset、halt、rd、wr、addr、data等端口的波形,更需要观察opcode、fetch、ir_addr、pc_addr等内部信号波形,因此需要用ModelSim SE 6.2b来观察其波形。CPU模块仿真波形如图4-47所示。

图4-47 CPU模块仿真波形

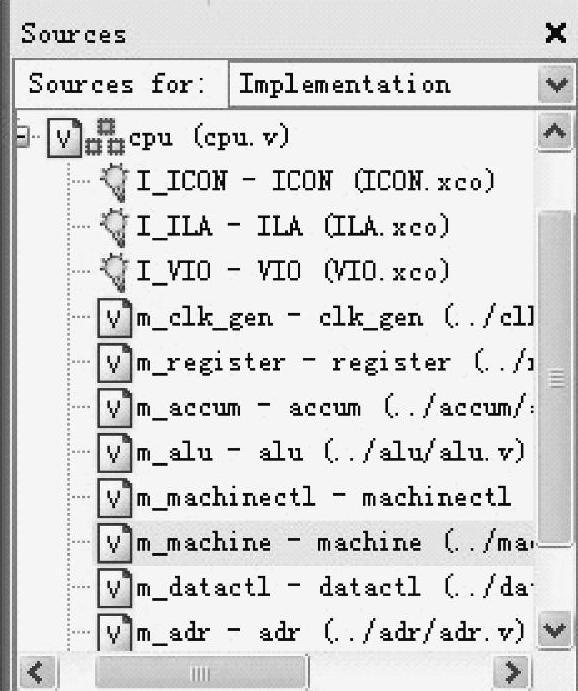

利用ChipScope在线调试,采用核生成法。由于要对模块进行实时的控制,因此在这里需要一个ICON核、一个ILA核、一个VIO核。将例化模块所用到的代码加到CPU相应的位置,并进行修改,最后得到调用核后的模块形式如图4-48所示。

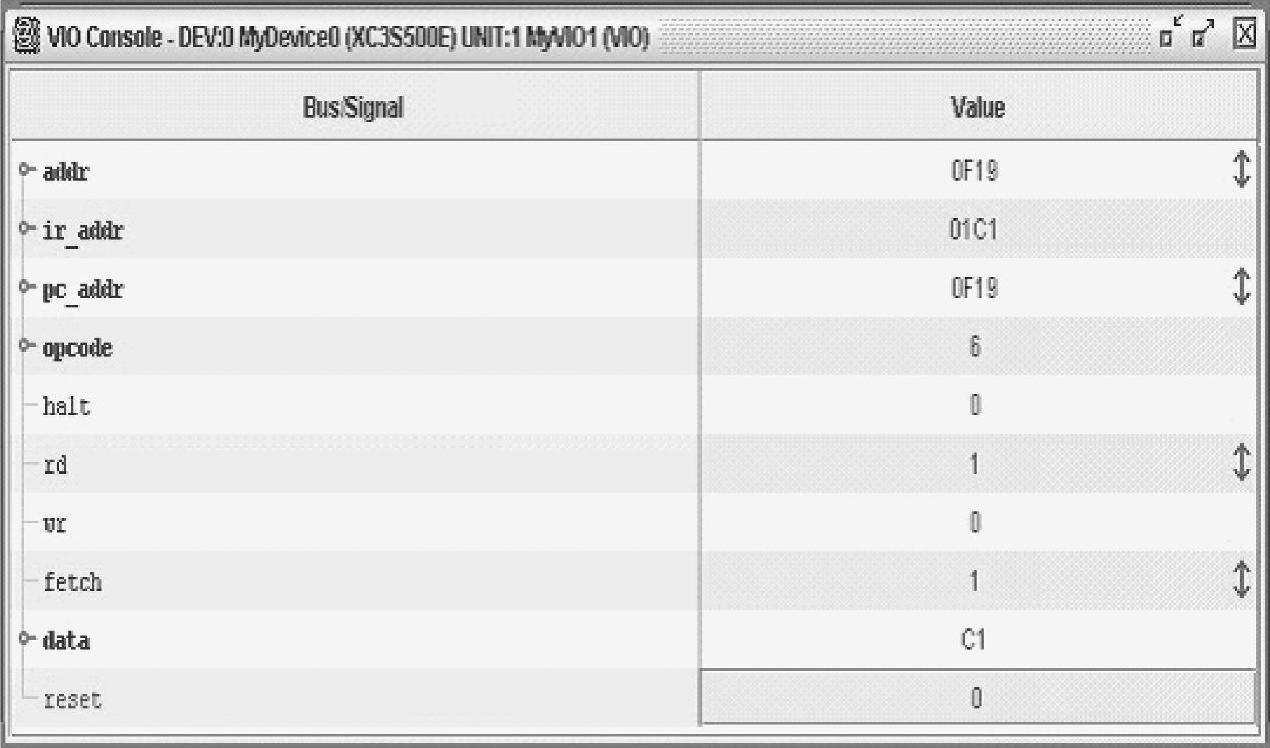

在实现步骤成功后,单击Generate Pro-gramming Files,生成bit流文件。双击Analyze Design Using Chipscope,出现chipscope Pro An-alyzer窗口。双击 图标,检测连接情况。然后下载bit流文件。双击VIO Console,可以看到异步输入信号在不停的变化着,如图4-49所示。

图标,检测连接情况。然后下载bit流文件。双击VIO Console,可以看到异步输入信号在不停的变化着,如图4-49所示。

(https://www.xing528.com)

(https://www.xing528.com)

图4-48 CPU的顶层文件及各子模块和调用的核

图4-49 VIO核调试结果

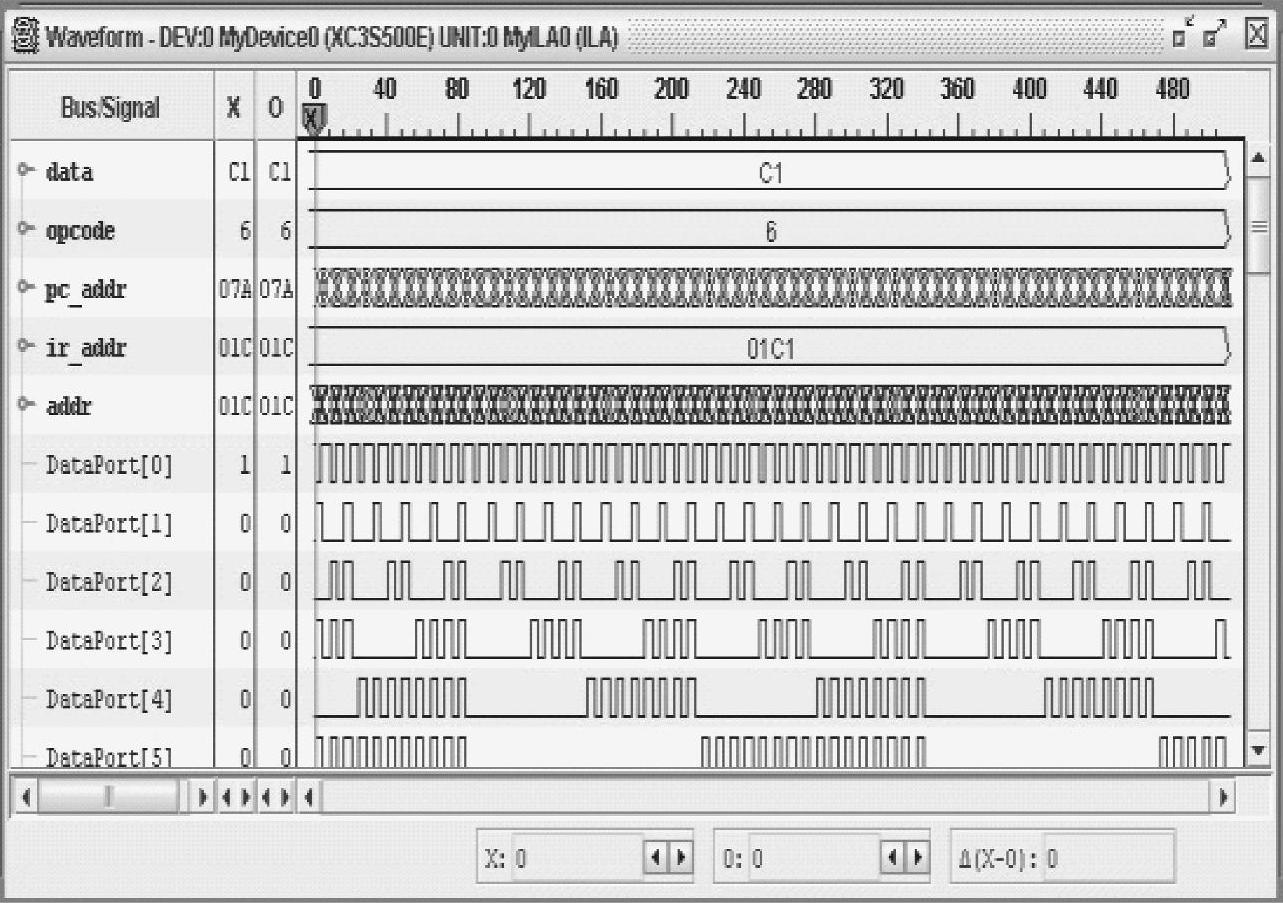

设置触发条件,然后双击 按钮,出现ILA核捕获的数据波形,如图4-50所示。

按钮,出现ILA核捕获的数据波形,如图4-50所示。

图4-50 ILA核调试结果

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。