控制器是RISC-CPU的核心部件,由它来控制指令有条不紊的工作。控制器件得到当前指令并进行译码,产生相应的控制信号送到时序和控制逻辑电路,从而合成外部电路所需要的时序和控制信号。这些信号送到CPU其他部件,以控制这些部件协调工作。CPU何时进行读指令、读写I/O端口、RAM区等操作,都是由状态机来控制的。

控制信号生成逻辑的功能如下:

(1)生成存储器的读/写信号。

(2)控制PC的赋值。在跳转指令时,PC的值由指令寄存器给出;其他情况下,由上一个值累加得到。

(3)将解码出的操作码送给数据通路ALU,控制ALU的运行。

(4)控制累加器是否要从总线上得到数据。

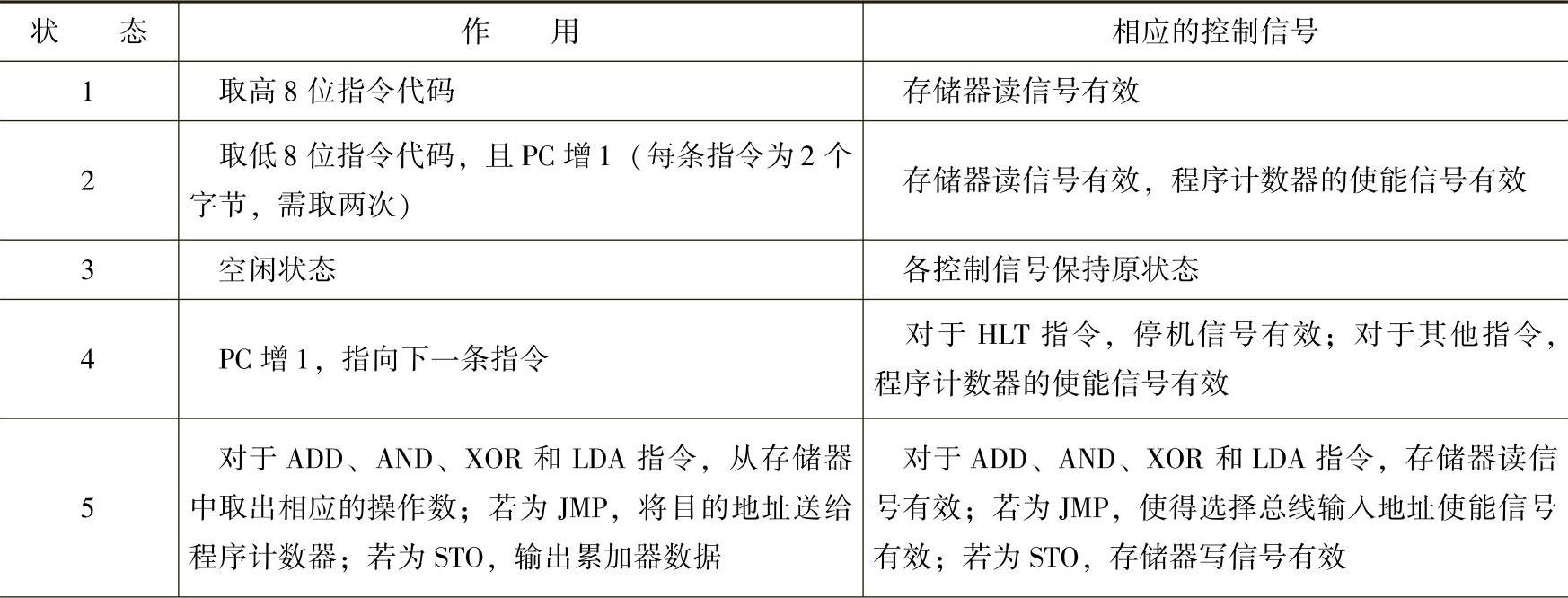

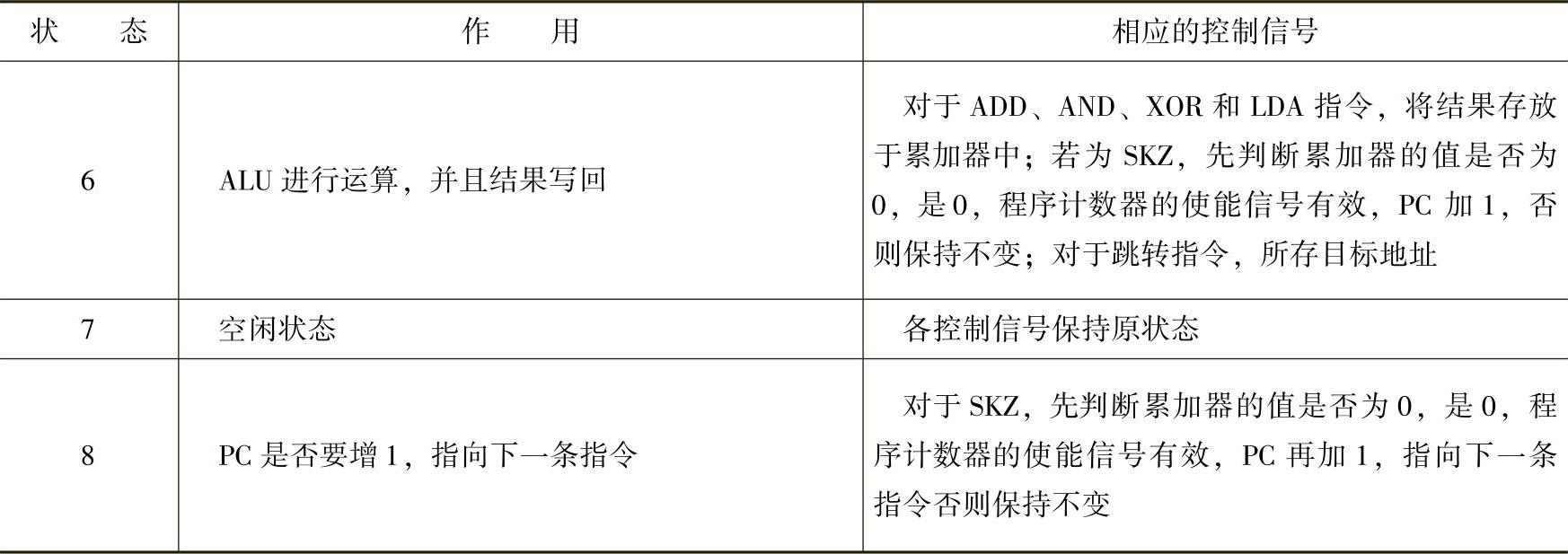

设计时要根据当前指令的类型和所处的周期来决定哪些控制信号有效。下面将一个完整的操作分成8个状态进行表示,各个状态的作用及控制信号如表4-3所示。

表4-3 RISC-CPU状态控制表

(续)

例如,对于ADD指令,控制时序信号如下:

第1个状态:存储器读信号有效,取高8位指令代码。

第2个状态:存储器读信号有效,取低8位指令代码,且PC增1。

第3个状态:将指令从数据上载入到指令寄存器中。

第4个状态:程序计数器使能信号有效,指示PC地址加1,指向下一条指令。(https://www.xing528.com)

第5个状态:存储器读信号有效,此时存储器地址取指令寄存器的地址,因此从存储器中读出的是M[addr]。

第6个状态:ALU计算A+M[addr],并将结果送到输出端。这时候累加器使能信号有效,准备好输出结果送到累加器中存放。

第7个状态:将ALU的结果锁存到累加器。

第8个状态:各个控制信号保持不变。

对于JMP指令,控制时序信号如下:

第1~第4个状态的控制信号与ADD指令一样。

第5个状态:使得选择总线输入地址使能信号有效,用指令寄存器的地址部分更新PC的值。

第6个状态:存目标地址。

第7~第8个状态:各个控制信号保持不变。

对于STO指令,控制时序信号如下:

第1~第4个状态的控制信号与ADD指令一样。

第5个状态:存储器写信号有效。

第6个状态:将累加器的值送到ALU的输出端。

第7~第8个状态:各个控制信号保持不变。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。