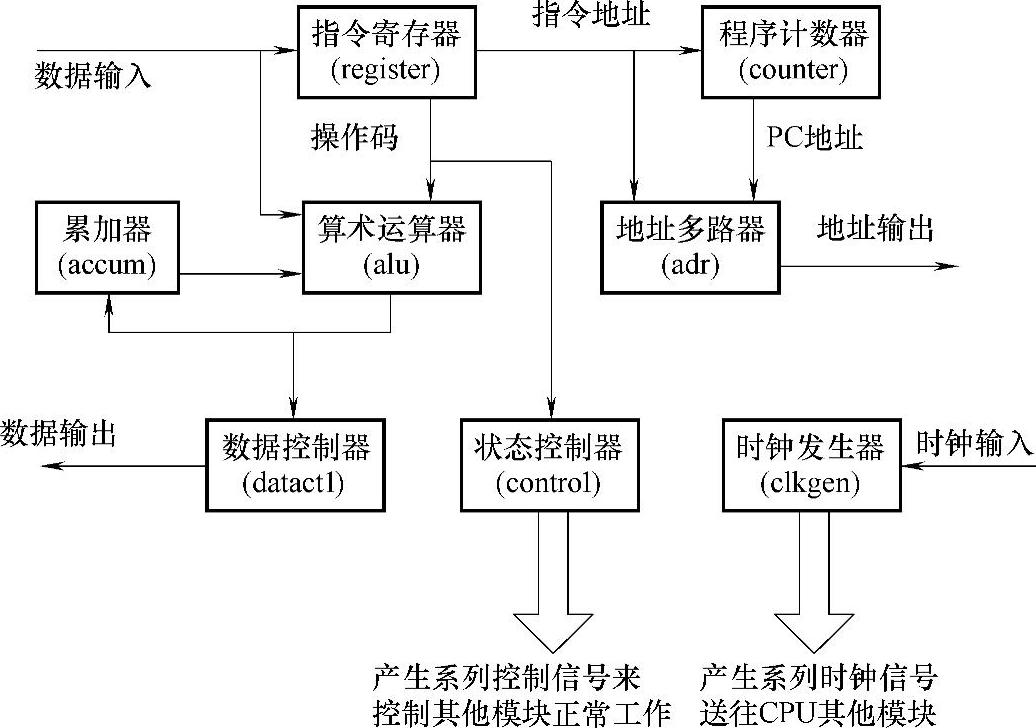

【摘要】:RSIC-CPU数据总线为8位,而每条指令为两个字节,所以每条指令需取两次。CPU的每次取到指令后,其状态控制器分析操作码后,产生一系列控制信号,启动或停止某些部件。其中时钟发生器利用外来时钟信号进行分频生成一系列时钟信号,送往其他部件用作时钟信号。其各个模块之间的关系如图4-23所示。

RSIC-CPU数据总线为8位,而每条指令为两个字节(高3位为操作码,低13位是地址),所以每条指令需取两次。CPU的每次取到指令后,其状态控制器(CPU的控制中心)分析操作码后,产生一系列控制信号,启动或停止某些部件。其中时钟发生器利用外来时钟信号进行分频生成一系列时钟信号,送往其他部件用作时钟信号。RISC-CPU是一个复杂的数字逻辑电路,但是它的基本部件的逻辑并不复杂,可把它分成以下8个基本部件:

(1)时钟发生器(clkgen) 产生一系列的时钟信号送往CPU其他部件;

(2)指令寄存器(register) 存储指令;

(3)累加器(accum) 存放ALU当前的结果,它也是算术逻辑运算单元双目运算中的一个数据来源;

(4)算术运算器(alu) 根据输入的8种不同操作码分别实现相应的加、与、读/写、异或、跳转等指令;

(5)数据控制器(datactl) 控制累加器的数据输出;

(6)状态控制器(control) CPU的控制核心,用于产生一系列的控制信号,启动或停止某些部件;(https://www.xing528.com)

(7)程序计数器(counter) 提供指令地址,以便读取指令;

(8)地址多路器(adr) 选择输出的地址是PC(程序计数)地址还是跳转的目标地址。

其各个模块之间的关系如图4-23所示。

图4-23 RISC-CPU结构图

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。