【摘要】:DDS是一种全数字化的频率合成器,由相位累加器、加法器、波形ROM、DAC和LPF构成。DDS原理框图如图3-1所示。图3-1 DDS原理框图图中,K为频率控制字,P为相位控制字,W为波形控制字,fc为时钟频率,N为相位累加器字长。可见K和时钟频率fc共同决定着DDS输出信号fout的频率值,它们之间的关系满足。由此可见,DDS相当于一个小数分频器。

DDS是一种全数字化的频率合成器,由相位累加器、加法器、波形ROM、DAC和LPF构成。输出信号的频率取决于频率控制字,频率分辨率取决于累加器位数,相位分辨率取决于ROM的地址线位数,幅度量化噪声取决于ROM的数据位字长和DAC位数。

DDS原理框图如图3-1所示。

图3-1 DDS原理框图

图中,K为频率控制字,P为相位控制字,W为波形控制字,fc为时钟频率,N为相位累加器字长。相位累加器在时钟的控制下做步长为K的累加,输出N位的二进制码与相位控制字P、波形控制字W相加后作为波形ROM的地址,对ROM表进行查找,得到波形的幅度。然后,经过DAC和LPF将数据转化成模拟波形。(https://www.xing528.com)

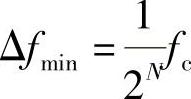

当DDS中的相位累加器计数大于2N时,相位累加器自动溢出最高位,保留后面的N比特数字于相位累加器中,即相当于做模余运算。可以看出,该相位累加器平均每2N/K个时钟周期溢出一次。可见K和时钟频率fc共同决定着DDS输出信号fout的频率值,它们之间的关系满足 。当K=1时,DDS为最小频率输出,DDS的最小频率分辨率为

。当K=1时,DDS为最小频率输出,DDS的最小频率分辨率为 。

。

由此可见,DDS相当于一个小数分频器。最小频率分辨率是频率控制字最低位为1、其余位均为0时DDS的输出频率,只要N足够大,即累加器有足够的长度,总能得到所需的频率分辨率,实际使用中计算出的K值很难为整数,因此不可避免地将会存在一定的频率误差。

由于ROM表的规模有限,相位累加器一般仅取高位作为寻址地址送入正弦查询表获得波形幅度值。正弦查询表中以二进制数形式存入用系统时钟对正弦信号进行采样所得的样值点,可见只需改变查询表内容就可实现不同的波形输出。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。