对各模块的仿真包括分频模块仿真、计数模块仿真、量程转换模块仿真、锁存模块仿真。

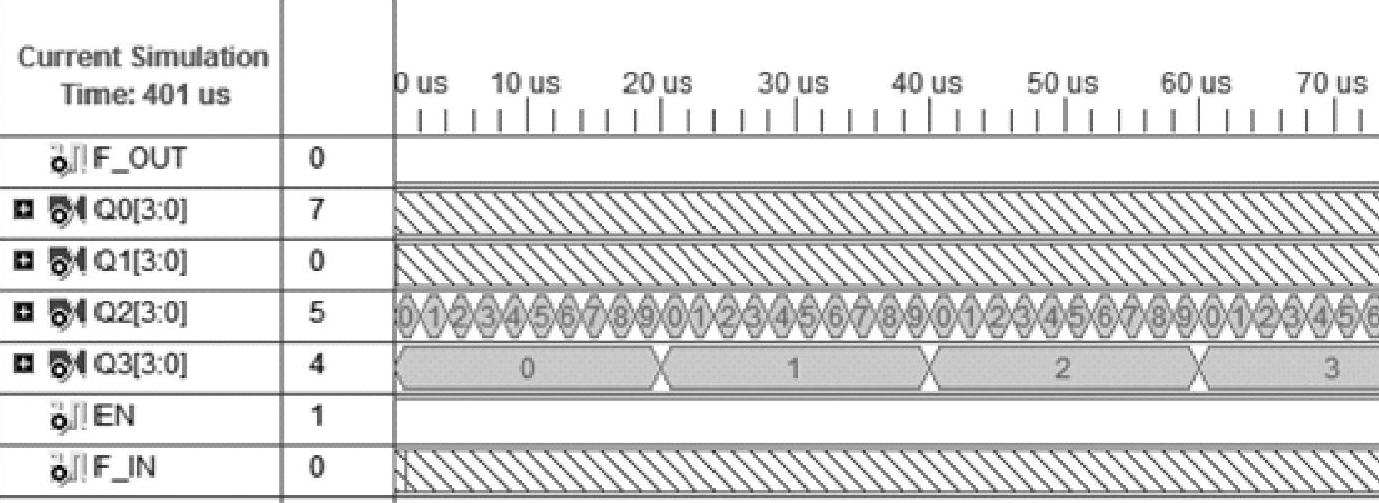

1.分频模块的仿真

分频模块是为了产生0.5Hz、5Hz、50Hz的信号,它们的周期分别为2s、0.2s、0.02s,即高电平时间为1s、0.1s、0.01s,把高电平当做闸门时间。

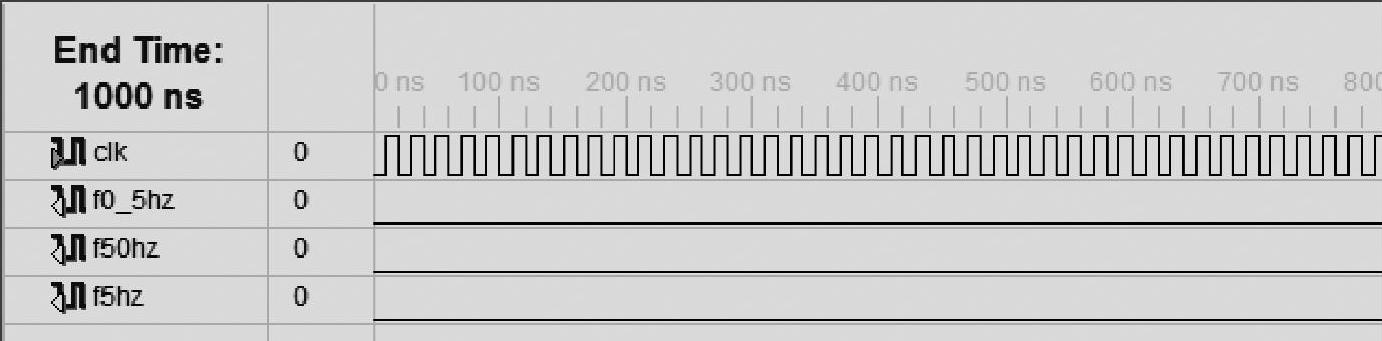

对分频模块进行功能仿真,添加test文件如图1-14所示,由图可知,输入的时钟信号clk的周期为20ns,即频率为50MHz,与后面板调的Spartan-3E系列板子的时钟信号一样。

图1-14 分频模块功能仿真波形编辑窗口

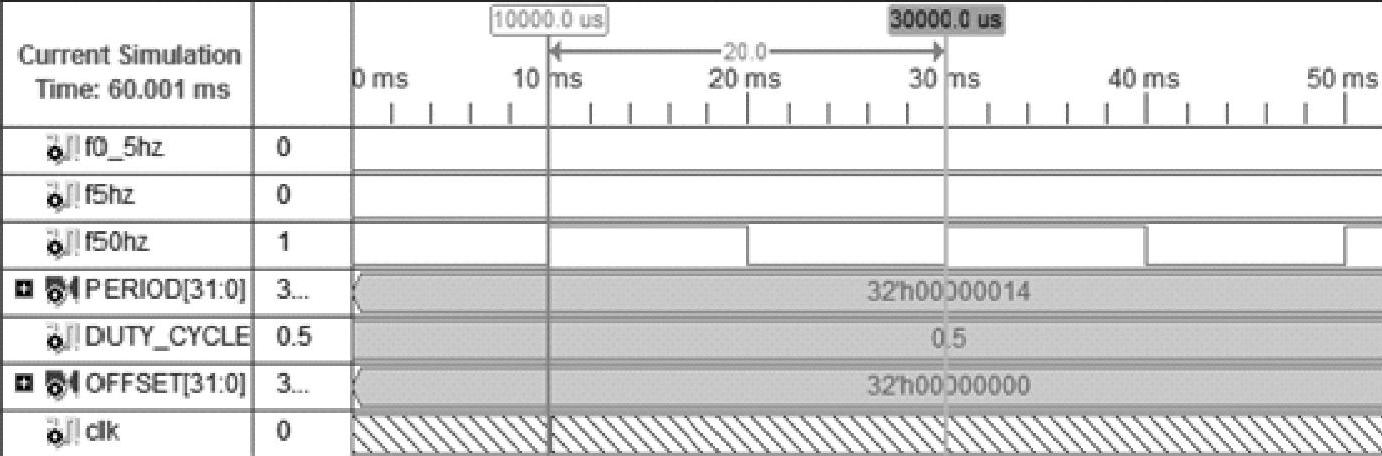

用ISE自带的仿真器进行功能仿真后,得到的结果如图1-15所示。

图1-15 分频模块功能仿真结果波形

(图中时间单位us应为μs,因图是从计算机下载,故均不改动)

由图1-15可以看出,分频后的波形f50Hz的周期为20ms,其频率为50Hz,恰好为50MHz的时钟频率进行1000000分频得到的频率,因此分频模块的功能仿真正确。

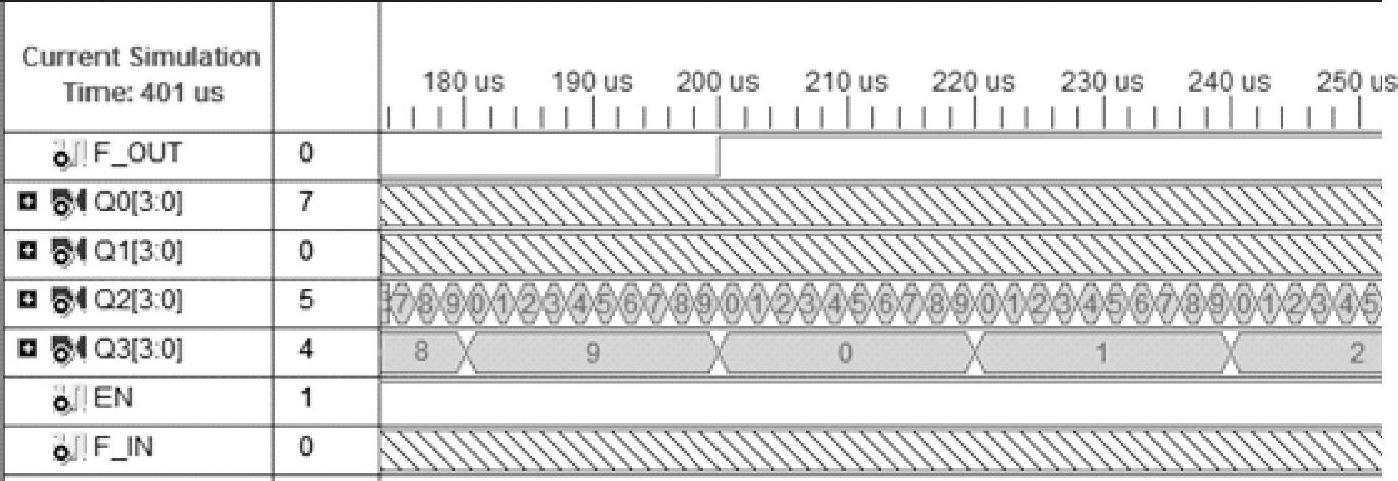

2.计数模块的仿真

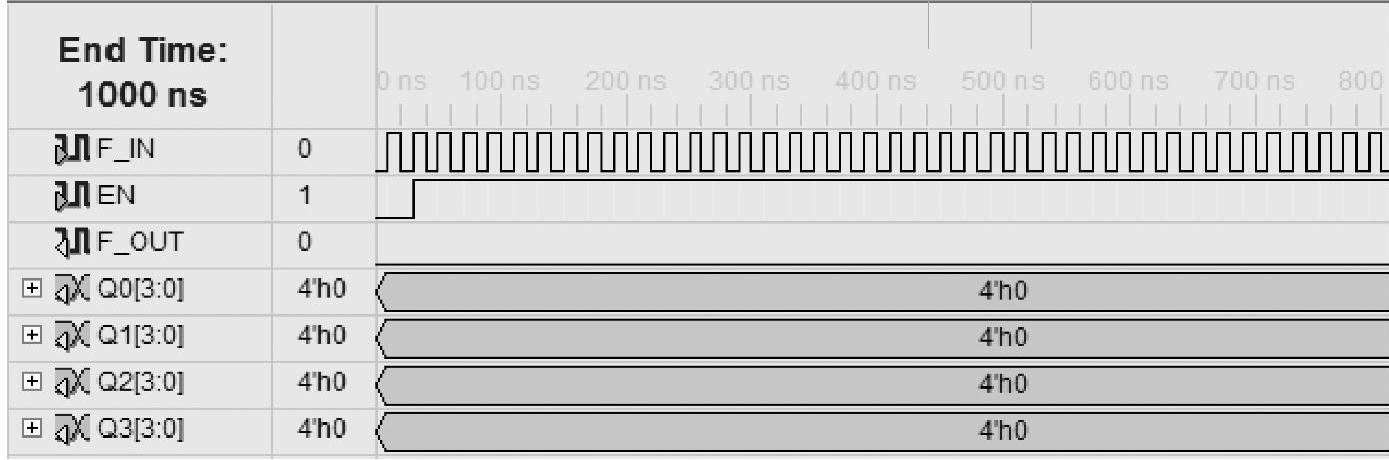

计数模块是为了实现在对被测信号的频率计数。对计数模块进行功能仿真,添加test文件如图1-16所示。所设置的输入被测信号的周期为20ns,频率为50MHz,这样方便观察波形。

图1-16 计数模块功能仿真波形编辑窗口

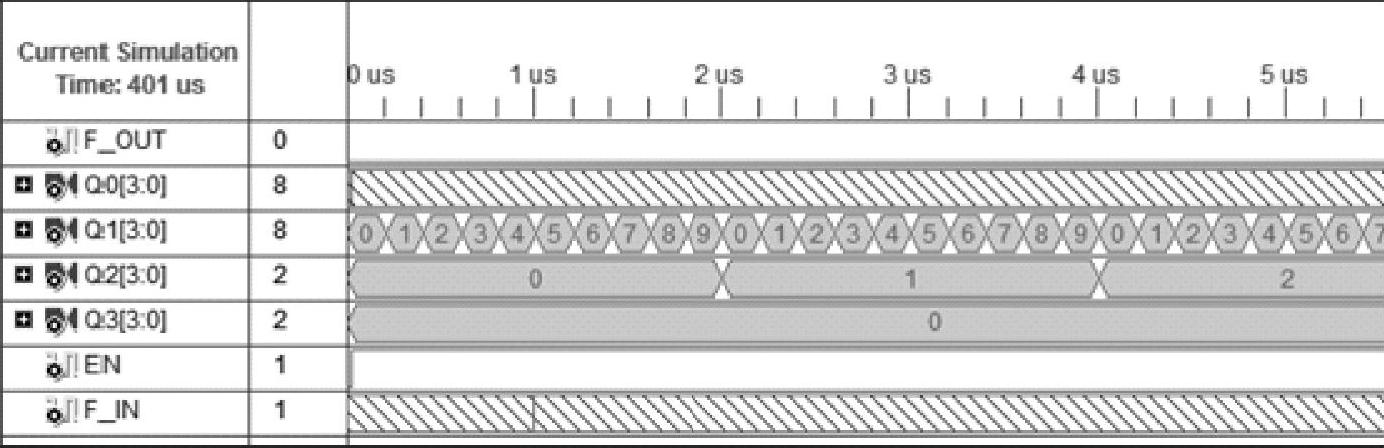

用ISE自带的仿真器进行功能仿真后,得到的结果如图1-17~图1-20所示。

图1-17 计数模块功能仿真结果波形1

由图1-17可以看出,每个外部脉冲到来时,个位Q0都进行加1操作,当Q0为9时,在下一个脉冲到来时,Q0就跳变成0,同时十位Q1加1。

图1-18 计数模块功能仿真结果波形2

由图1-18可以看出,当Q1、Q0同时为9时,在下一个脉冲到来时,Q1、Q0就跳变成0,同时百位Q2加1。

由图1-19可以看出,当Q2、Q1、Q0同时为9时,在下一个脉冲到来时,Q2、Q1、Q0同时跳变成0,同时千位Q3加1。

由图1-20可以看出,当Q3、Q2、Q1、Q0同时为9时,在下一个脉冲到来时,Q3、Q2、Q1、Q0同时跳变成0,同时溢出位FOUT置1。

(https://www.xing528.com)

(https://www.xing528.com)

图1-19 计数模块功能仿真结果波形3

图1-20 计数模块功能仿真结果波形4

由以上仿真结果可以看出,计数模块的功能仿真正确。

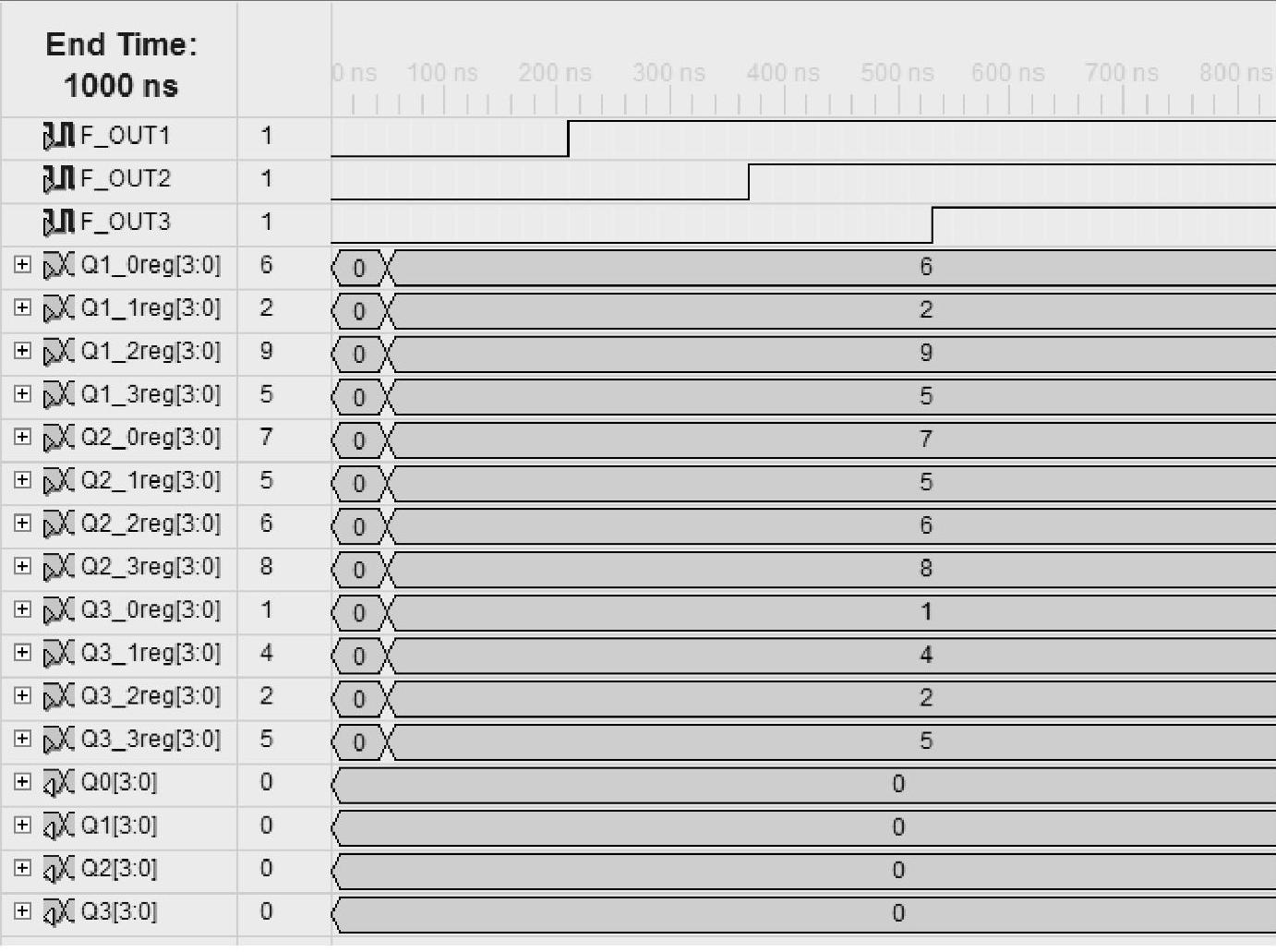

3.量程转换模块的仿真

量程转换模块是为了实现在不同的频率范围内采用不同的量程进行测量的功能。

当1M挡的溢出标志F_OUT3为1时,不管F_OUT1、F_OUT2是什么值,输出Q0、Q1、Q2、Q3均为高阻态。当1M挡的溢出标志F_OUT3为0,而100k挡的溢出标志为1时,就将1M挡的计数值Q3_0reg、Q3_1reg、Q3_2reg、Q3_3reg作为输出,即输出Q0、Q1、Q2、Q3值为Q3_0reg、Q3_1reg、Q3_2reg、Q3_3reg的值。当1M挡、100k挡的溢出标志F_OUT3、F_OUT2都为0,而10k挡的溢出标志F_OUT1为1时,就将100k挡的计数值Q2_0reg、Q2_1reg、Q2_2reg、Q2_3reg作为输出,即输出Q0、Q1、Q2、Q3值为Q2_0reg、Q2_1reg、Q2_2reg、Q2_3reg的值。当1M挡、100k挡、10k挡的溢出标志F OUT3、F_OUT2、F_OUT1都为0时,就将10k挡的计数值Q1_0reg、Q1_1reg、Q1_2reg、Q1_3reg作为输出,即输出Q0、Q1、Q2、Q3值为Q1_0reg、Q1_1reg、Q1_2reg、Q1_3reg的值。

对量程转换模块进行功能仿真,添加test文件如图1-21所示。

用ISE自带的仿真器进行功能仿真后,得到的结果如图1-22所示。

由图1-22可知,当F_OUT1、F_OUT2、F_OUT3均为0时,输出Q0、Q1、Q2、Q3的值即为Q1_0reg、Q1_1reg、Q1_2reg、Q1_3reg的值。当F_OUT1为1,且F_OUT2、F_OUT3为0时,输出Q0、Q1_、Q2_、Q3_的值即为Q2_0reg、Q2_1reg、Q2_2reg、Q2_3reg的值。当F_OUT2为1,且F_OUT3为0时,输出Q0、Q1、Q2、Q3的值即为Q30reg、Q3_1reg、Q3_2reg、Q3_3reg的值。当F_OUT3为1时,输出Q0、Q1、Q2、Q3的值为高阻态。因此,量程转换模块的功能仿真正确。

图1-21 量程转换模块功能仿真波形编辑窗口

图1-22 量程转换模块功能仿真结果波形

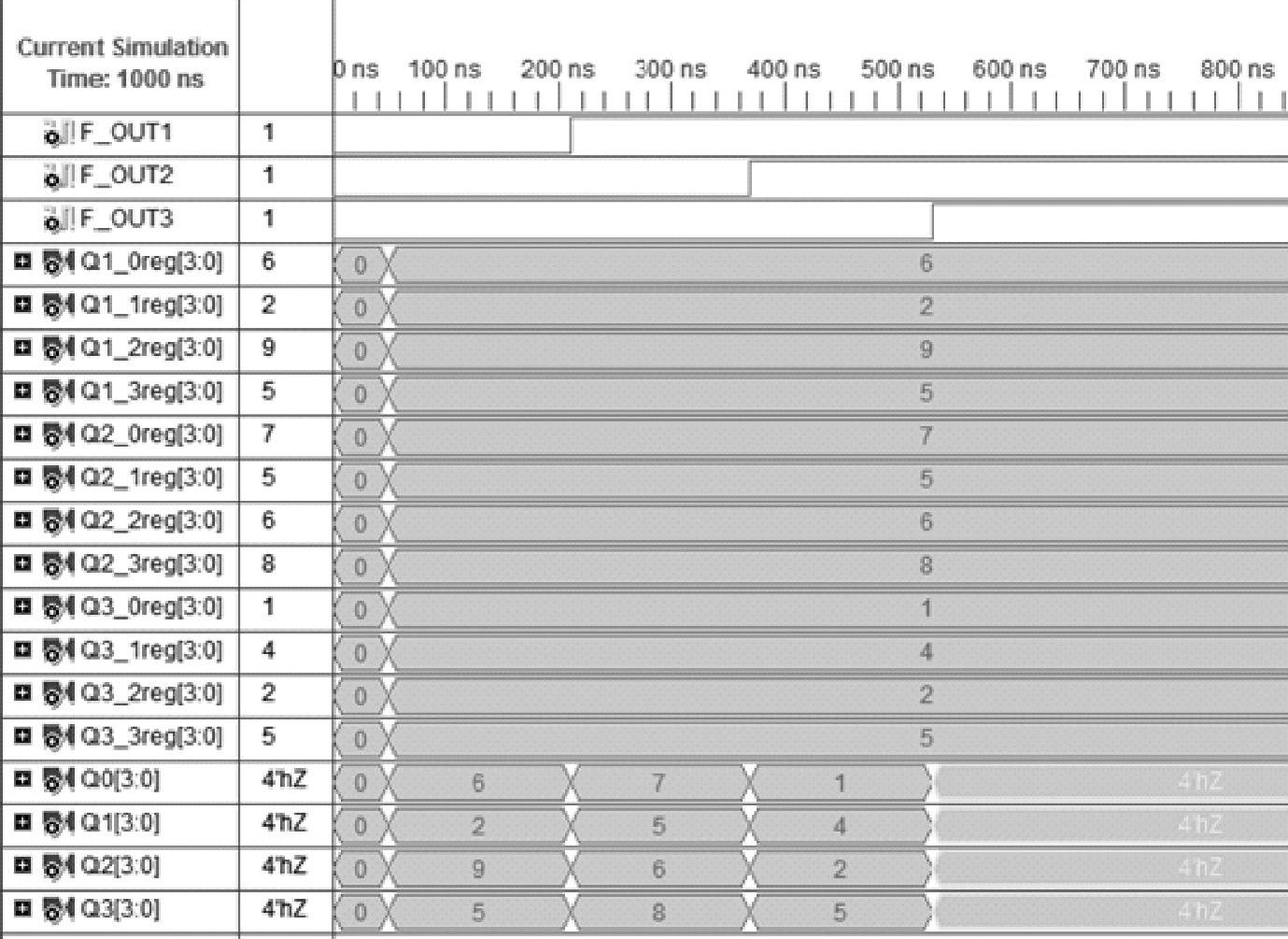

4.锁存模块的仿真

闸门信号由高电平变到低电平时,将测量得到的计数结果保存到寄存器里面。

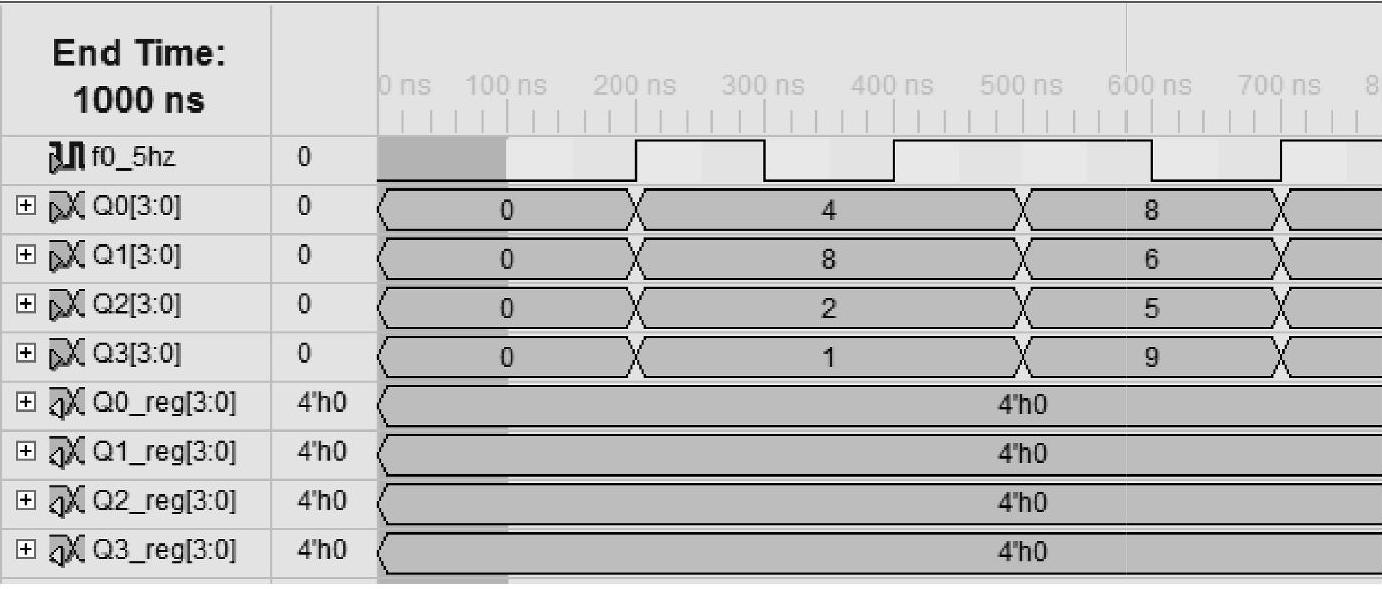

对计数模块进行功能仿真,添加test文件如图1-23所示。在这里,对触发信号(闸门信号)f05Hz进行了无规则的设置。

图1-23 锁存模块功能仿真波形编辑窗口

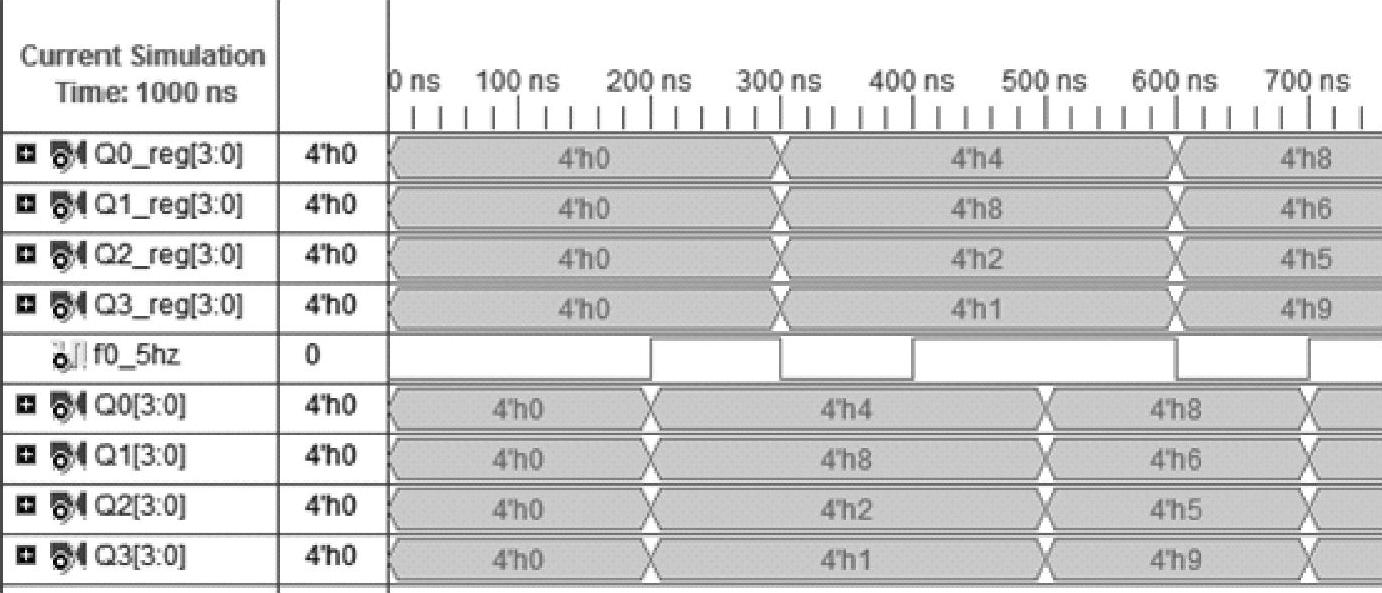

用ISE自带的仿真器进行功能仿真后,得到的结果如图1-24所示。

图1-24 锁存模块功能仿真结果波形

由图1-24可知,在触发信号f05Hz下降沿到来时,Q0、Q1、Q2、Q3的值赋值给Q0_reg、Q1_reg、Q2_reg、Q3_reg。因此,锁存模块的功能仿真正确。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。