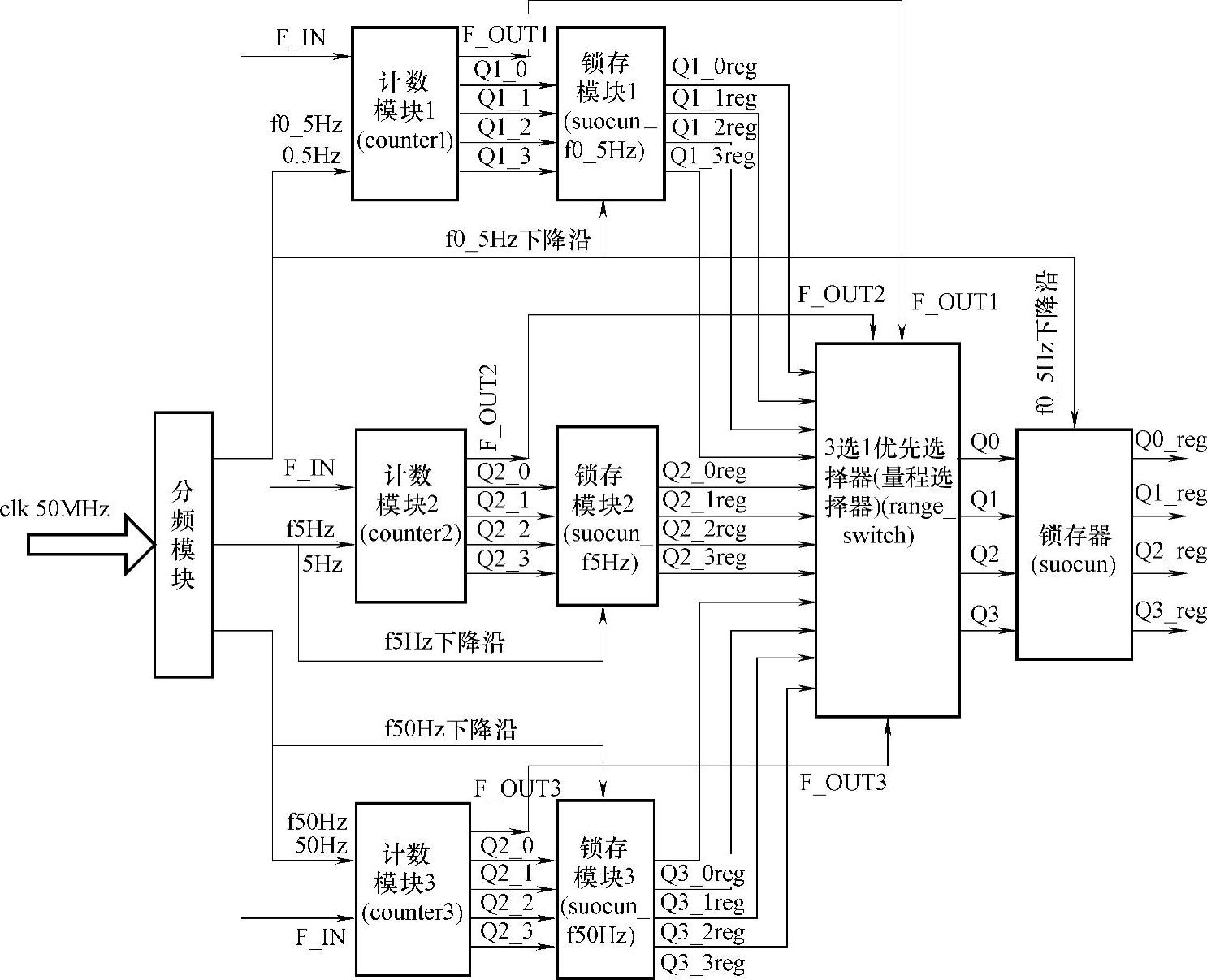

用FPGA来实现自动换量程频率计的设计,需要对其进行细化,将系统分成如下五个模块:控制模块、分频模块、计数模块、量程转换模块、锁存模块。通过对图1-2所示的基本原理图进行深入分析,可得到如图1-3所示的更加直观的原理框图。

对图1-3所示原理框图介绍如下:

(1)50MHz的时钟信号经过分频器得到三个不同的频率f05Hz、f5Hz、f50Hz,它们的频率分别为0.5Hz、5Hz、50Hz,这三个频率作为闸门信号输入到计数器。三个计数器在闸门信号的上升沿到来时开始对被测信号FIN进行计数。当闸门信号的下降沿到来时,计数结束,并且将所记的数据分别锁存起来。在计数过程中,若计数数值超过9999,则产生溢出信号,使溢出标志置1。

(2)将计数后锁存的数据输入到量程选择器,该量程选择器在判断三个计数器的溢出标志基础上选择不同计数器的数据进行输出。量程选择器的具体工作原理:若计数器3的溢出标志FOUT3为1,则输出为高阻态;若计数器3的溢出标志FOUT3为0,而计数器2的溢出标志FOUT2为1,则量程选择器的输出为计数器3的计数结果,但是被测频率值为计数器3的计数结果乘以100;若计数器3、2的溢出标志FOUT3、FOUT2为0,而计数器1的溢出标志FOUT1为1,则量程选择器的输出为计数器2的计数结果,但是被测频率值为计数器2的计数结果乘以10;若计数器3、2、1的溢出标志FOUT3、FOUT2、F OUT1都为0,则量程选择器的输出为计数器1的计数结果,这时被测频率值就为计数器1的计数结果。量程选择器的输出数据输入到锁存器,在0.5Hz信号的下降沿到来时,将数据锁存起来,这样所测的频率就能清楚地通过译码电路显示出来了。(https://www.xing528.com)

需要说明的是,本设计过程中设计了三个量程,分别为10k挡、100k挡、1M挡。其中,1s的闸门时间对应的计数器为10k挡,0.1s的闸门时间对应的计数器为100k挡,0.01s的闸门时间对应的计数器为1M挡。另外,由于本设计只涉及FPGA,因此没有考虑模拟信号的频率测量,也没有考虑译码显示电路的设计。如果要测量模拟信号的频率,只需在计数模块前加上一个信号整形电路,将输入的模拟信号转换成脉冲矩形信号,再进行计数即可。

图1-3 基于FPGA的自动换量程原理框图

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。