【摘要】:串行外设接口是一种高速的、全双工、同步的通信总线,并且在芯片的管脚上只占用四根线。SPI传输需要4根接线SCLK、SSEL、MISO和MOSI。图7.23SPI传输接口SPI支持4种工作模式,由时钟极性和时钟相位决定传输所选用的模式,如图7.24所示。图7.24SPI的四种传输模式本章中选用DSP2812作为SPI通信的Master,FPGA作为SPI通信的Slaver。设置时钟极性CPOL=0和时钟相位CPHA=0,即时钟的空闲电平为低电平、在每个周期的第一个时钟沿采样,要求在SSEL下降沿时就发送第一个数据。

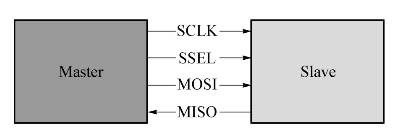

串行外设接口(serial peripheral interface,SPI)是一种高速的、全双工、同步的通信总线,并且在芯片的管脚上只占用四根线。SPI传输需要4根接线SCLK、SSEL、MISO和MOSI。其中,SCLK是由Master提供传输的时钟,SSEL提供传输的使能信号(低电平有效),MISO使数据从SLAVE传输到Master,MOSI使数据从Master传输到Slave[10],如图7.23所示。

图7.23 SPI传输接口

SPI支持4种工作模式(SP0,SP1,SP2,SP3),由时钟极性(CPOL)和时钟相位(CPHA)决定传输所选用的模式,如图7.24所示。CPOL用来决定SCK时钟信号空闲时的电平,CPOL=0,空闲电平为低电平;CPOL=1时,空闲电平为高电平。CPHA用来决定采样时刻,CPHA=0,在每个周期的第一个时钟沿采样;CPHA=1,在每个周期的第二个时钟沿采样。在CPHA=0时,要求在SSEL下降沿时就发送第一个数据。(https://www.xing528.com)

图7.24 SPI的四种传输模式

本章中选用DSP2812作为SPI通信的Master,FPGA作为SPI通信的Slaver。设置时钟极性CPOL=0和时钟相位CPHA=0,即时钟的空闲电平为低电平、在每个周期的第一个时钟沿采样,要求在SSEL下降沿时就发送第一个数据。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。