采用电压斩波控制方式的开关磁阻电机控制系统的实质就是调节PWM的输出波形,通过调节PWM占空比来实现对电机相电流的控制。在PWM斩波控制中,在DSP硬件允许的情况下,尽可能地提高PWM的频率来降低SRM的振动和噪声,但同时也应该兼顾功率开关原件的工作频率限制,并且考虑由此带来的电路系统的复杂度。

TMS320F2812型DSP控制器把具有低功耗、高性能处理能力的CPU加强结构设计与为电机运行控制应用优化的几个先进外围设备结合在一起。这些外围设备包括了事件管理器(EV)模块和一个双十位模数转换器(ADC)。

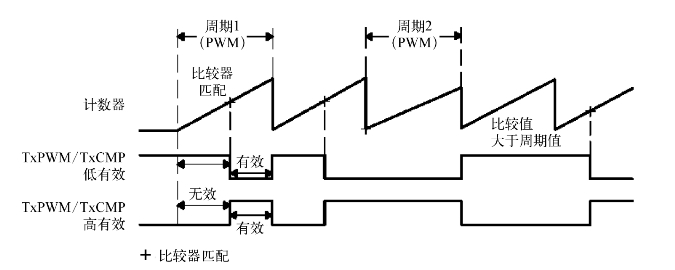

EV模块提供了大量的函数和功能部件,使得用先进控制技术来实现SRM的高精度、高效、全变速控制成为可能。EV模块通过提供通用(GP)定时器和比较寄存器可以产生多达12个PWM输出。按照EV模块的功能引脚,这些PWM输出的来源可以分成三类:①通过3个GP定时器产生PWM输出;②通过EV模块的全比较单元产生PWM输出;③利用EV模块的简单比较单元产生PWM输出。其中EV模块中有3个全比较单元(全比较单元1、2和3),每个全比较单元有两个相应的PWM输出。全比较单元的时间基准由GP定时器1提供。本章中样机系统采用EV模块的全比较单元来产生SRM系统电流斩波PWM的输出。其中定时器按照寄存器TxCON中的TMODE0、TMODE1位来确定比价器的工作模式。本节采用连续递增计数模式,如图7.12所示。当设置比较输出为低有效的状态时,计数器的初始计数值小于比较寄存器内预先的比较值,此时比较无效,比较输出为高电平;当计数器的计数值大于比较值时,比较有效,比较输出为低电平。

(https://www.xing528.com)

(https://www.xing528.com)

图7.12 PWM的比较输出

利用EV模块内部全比较单元和相应的电路产生PWM波形,可以将CPU的开销和用户的干预降至最小,对全比较动作控制寄存器(ACTR)的操作可以使相应的控制变得非常简单容易。将ACTR配置为在每个PWM周期都对比较寄存器(CMPRx)进行重新加载,从而调整输出PWM波的占空比。

本节基于DSP的SRM系统的PWM输出电路如图7.13所示,图中仅展示了相关的部分电路。电路中,从DSP2812输出的9路3.3 V的PWM信号经过74HC245变成IGBT驱动器所需的5 V的PWM信号。另外在PWM输出电路上还增加了为保护系统而提供的PWM输出截止控制信号OE,以便于在系统出现意外的情况下,控制电路能够快速地截止PWM的输出,从而保护驱动电路和SRM。OE由过流、过压和过热信号的逻辑或得出。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。