IEEE754—1985标准中定义的单精度浮点数据的格式为

式中,s为数据位;e为指数;ƒ为尾数。

单精度浮点格式的数据长度为32 bit,其中共有三段:符号位、指数域和尾数域,它们的长度分别为1 bit、8 bit和23 bit。

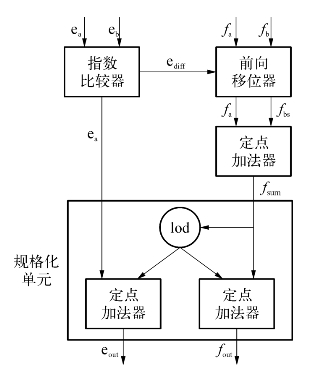

图4.11 浮点加法器的结构

本程序中主要包含浮点数的浮点加、乘运算。在此详细介绍浮点加法器在FPGA中的实现。FPGA的浮点加法器结构如图4.11所示。

首先将ea、eb送入指数比较器进行比较,得到阶差ediff,前移位器将指数较小的那个数的尾数右移ediff位,得到新的尾数ƒbs,然后将ƒbs送入定点加法器进行尾数相加。如果尾数相加产生了进位,那么把和右移一位,指数加1。用规格化单元对结果进行规格化。在规格化单元里有一个前导1检测电路(leading-one-detector),可以检测出尾数中第一个1的位置,后移位器根据此位置对尾数进行左移,同时指数减去相应的值。

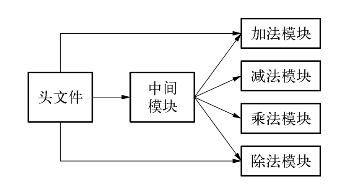

图4.12 CMAC程序设计的HDL结构(https://www.xing528.com)

为了便于管理和阅读程序,将程序中需要被多次调用的加法、减法、乘法和取整运算编程为四个子模块,以实现模块化编程。主程序的结构如图4.12所示。

中间模块通过对上述加、减、乘、除四个模块的调用从每一层存储空间中提取源程序中的电感L。程序的头文件实现对中间模块的调用,并且对中间模块提取的每层电感值进行求和,最后得到指定条件下的电感值。

FPGA芯片选用Altera公司Cyclone系列的EP2C8Q208C,速度等级为8。该芯片具有20 060个逻辑单元(LE)、4个专用的锁相环PLL、208个可配置的IO端口和高达288 k B的片上RAM。

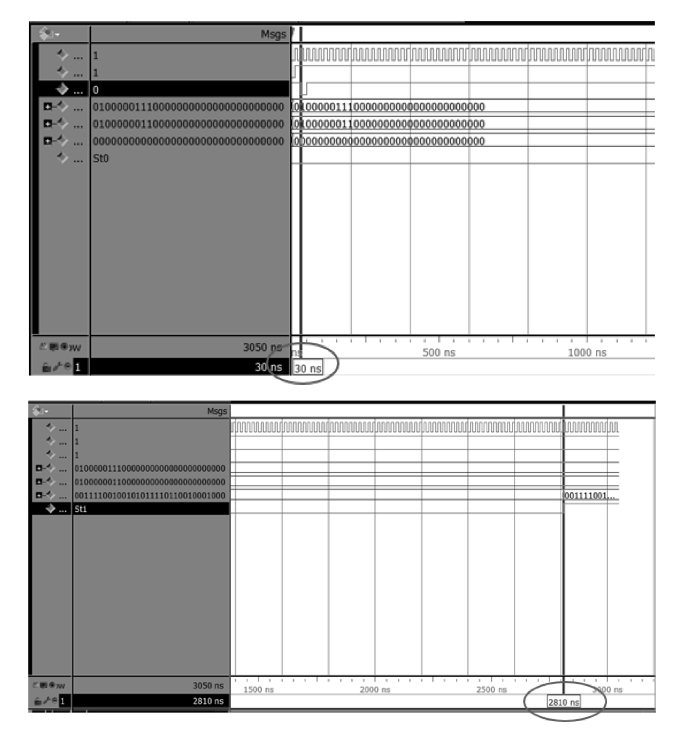

将相绕组电流采样、编码器位置采样数值经离线CMAC训练后得到的CMAC模型进行FPGA在线验证。取

a=32’b0_1000_0011_10000000000000000000000; //位置角 十进制数字24

I=32’b0_1000_0001_10000000000000000000000; //电流 十进制数字6

则FPGA硬件并行运算实现的时序如图4.13所示。

图4.13 CMAC的硬件计算延时

从图4.13中可以看出,FPGA实现电感计算的总用时为2.8μs。相对于100μs的闭环控制环,基于FPGA硬件计算模型的电感在线计算方法能够满足高精度和实时性要求。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。